题材新闻:

2025年10月2日,三星电子、SK海力士与OPEN AI的星际之门项目达成初步供货协议。

2025年9月20日,三星、美光等大厂计划四季度上调DDR5/LPDDR5价格15%-30%。

题材介绍:

一、半导体存储:数据的蓄水池

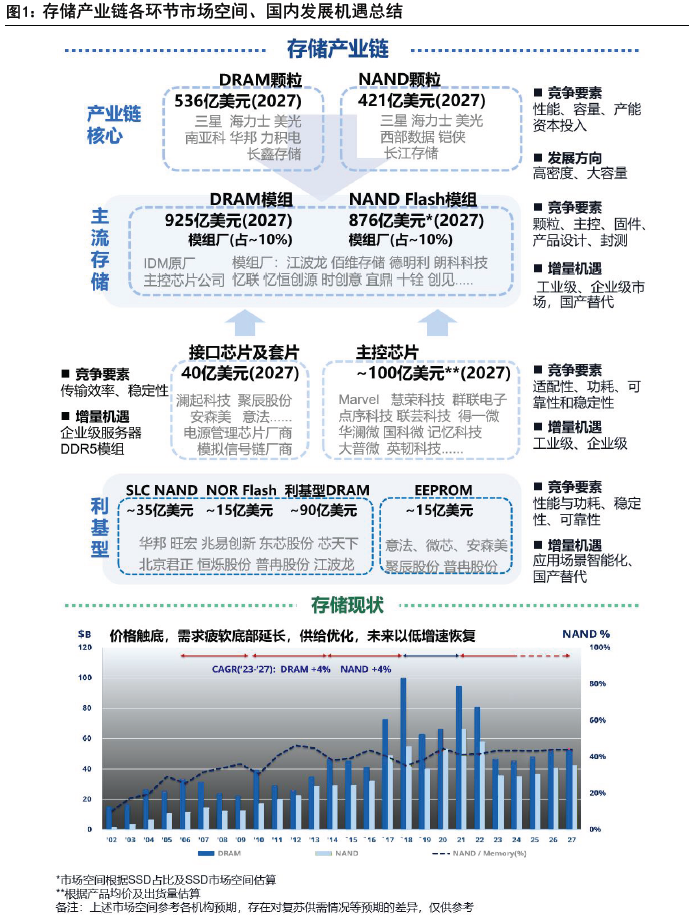

1、存储产业链

存储器是指利用磁性材料或半导体等材料作为介质进行信息存储的器件。半导体存储器利用半导体介质贮存电荷以实现信息存储,存储与读取过程体现为电荷的贮存或释放,半导体存储是集成电路的重要分支。

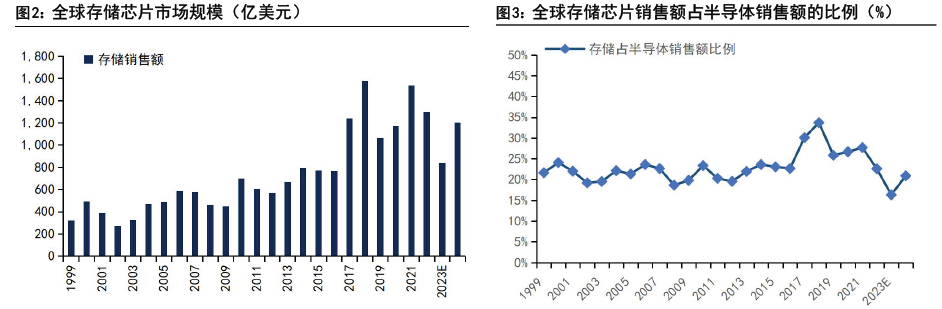

根据世界半导体贸易统计组织(WSTS)数据,2022年全球集成电路产业规模为 4744.02亿美元,其中存储芯片规模为1297.67 亿美元,约占集成电路产业总体规模的 22.6%,与逻辑芯片共同构成集成电路产业的两大支柱。

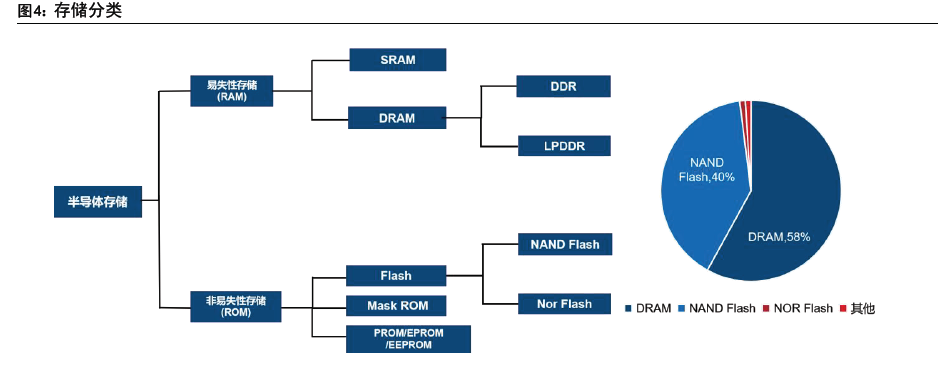

2、存储分类

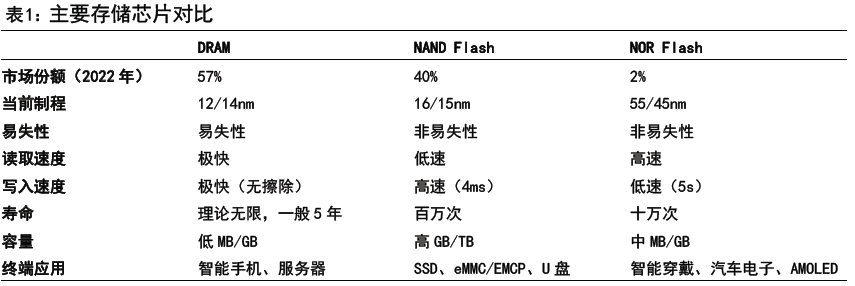

存储芯片作为全球半导体行业第一大细分领域可分为易失性和非易失性两类,易失性存储又可分为动态随机存储 (DRAM)和静态随机存储 (SRAM)。

其中DRAM具备集成度高、低功耗、低成本、体积小等显著优势,通常用于智能手机及服务器内存。非易失性存储主要包括NAND FLASH和NOR FLASH,其中NAND被广泛用于SSD、eMMC/EMCP、U盘等高端大容量产品,NOR则主要用于智能穿戴、汽车电子、AMOLED等领域。

1)易失性存储(RAM)

易失性存储是运行程序临时数据的存储媒介,供CPU读写处理,占存储市场的57%,RAM需要维持通电以临时保存数据供主系统CPU读写和处理。

由于RAM可以实现对数据的高速读写,可作为操作系统或其他正在运行中的程序的临时数据存储媒介,在此基础上,RAM根据是否需要周期性刷新以维持数据存储,进一步分为动态随机存取存储器 (DRAM)和静态随机存取存储器 (SRAM)。

动态随机存取存储器(DRAM)需要在通电状态下通过周期性刷新来维持数据,静态随机存取存储器(SRAM)则不需要周期性刷新。SRAM的速度更快、耗电量较低但存储器容量较低且制造成本较高,通常用于缓存;DRAM 的成本更低,密度更大,主要用作主处理器存储器。

2)非易失性存储(ROM)

非易失性存储主要指只读存储器 (ROM),无需持续通电亦能长久保存数据的存储器,占存储市场的43%。

ROM包括掩膜只读存储器 (Mask ROM)、可编程只读存储器(PROM)、可编程可擦除只读存储器 (EPROM)、电可擦除可编程只读存储器 (EEPROM)和快闪存储器 (Flash)等不同阶段产生的产品。

Flash 作为主要应用包括NAND Flash和NOR Flash;NAND Flash (占40%)是一种半导体单元串联排列的闪存,其闪存单元垂直排列,可实现大容量化;同时无需记忆各单元的位置,写入速度很快。

由于其小型化和大容量化,NAND闪存常常被用作各种移动设备和电子产品的存储设备,是目前全球市场大容量非易失存储的主流技术方案。

NOR Flash是一种半导体单元并联排列的闪存由于并联排列的它的数据检索快读取速度快且数据安全性高;但NOR由于要记住各个单元的地址电路较为复杂储存数据的空间小,很难实现大容量化,在小容量场景中具备经济效益。

二、未来存储发展方向:高密度、大容量

1、从平面到4D,NAND存储密度不断提升

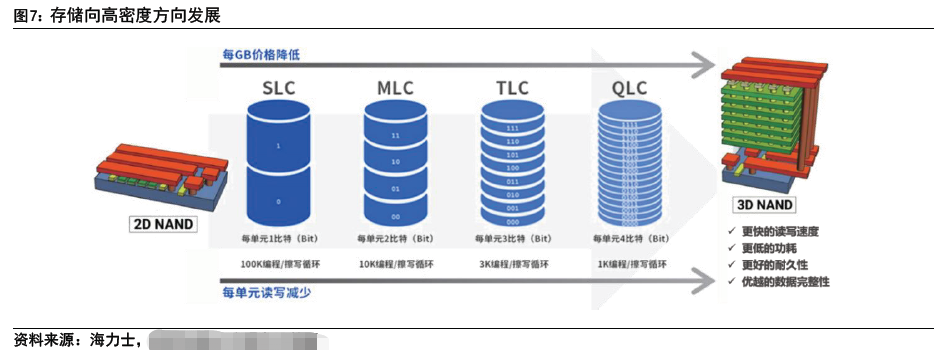

提高存储单元的可存储数位 (bit)量和提升3D NAND Flash 的堆叠层数是存储密度提升的主要方式。

NAND Flash 的进化过程中最重要的趋势就是每个单元拥有更高的密度,从Single Level Cell(SLC)对应1bit、Multi Level Cell(MLC)对应2bit、Triple Level Cell(TLC)对应 3bit到Quadruple Level Cell(QLC)对应4bit 发展,存储密度得到提升。

但由于在 2D 形式下,单位存储单元密度提升会带来擦写次数减少、可靠性降低和单元间干涉现象严重等问题,3D NAND 技术应运而生。

3D NAND 大幅减少了单元 (CelI) 之间的干扰影响,提高了单元自身的特性,并持续提高积层单数就能够实现数据容量的扩大及成本节约,其读写速度、功耗、成本、耐久性、数据传输速度及容量等均展现出卓越的优势。

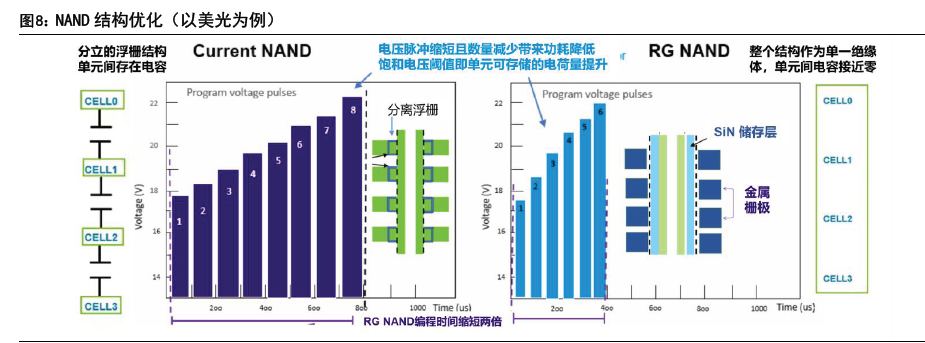

为提升性能和容量,3DNAND的存储单元基本结构从浮栅结构FG逐步升级。以美光为例,当3DNAND通过创建垂直单元堆栈实现空间缩小,而单元间产生的电容合导致编程时间增加或性能降低时,美光设计了RG NAND结构。

通过加入一层非导电的氮化硅(SiN)层充当存储电荷的绝缘体,减轻了电容合;利用金属作为控制栅极以延长使用寿命;最终读取和擦除速度比当前3DNAND快两倍。

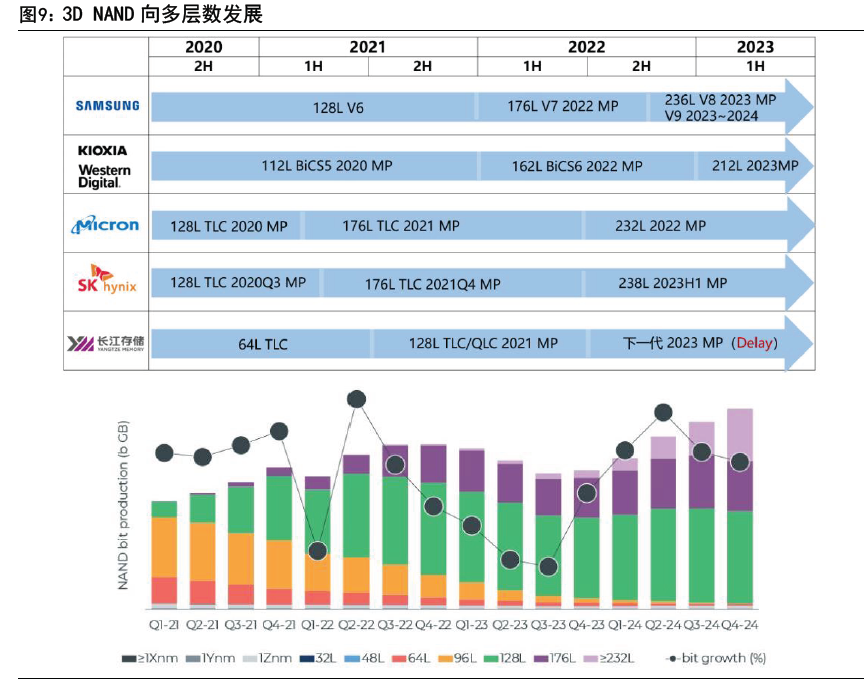

3DNAND为闪存市场主流产品,22年应用占比超80%,随存储密度要求提升层数增加。自2013年后,3D NAND 的堆叠层数出现了快速增长。

2015年推出了48层NAND,2017年推出64 层,2019年96层,2020年128层,2021年176层,2022年232层。目前,三星、美光、SK 海力士、长江存储等均超过了200层。根据 Yole数据128层NAND仍为主要工艺232层NAND将随数据中心等需求增加加速渗透。

2、从1X到1Z,DRAM制程不断缩小

DRAM占据全球存储器市场第一大份额,手机和服务器推动DRAM 市场需求扩大。

DRAM按照产品分类可分为DDR/LPDDR/GDDR和传统型(Legacy/SDR)DRAM,其中DDR(DDR SDRAM 双倍数据速率同步动态随机存取存储器)是DRAM应用最广的产品类型。

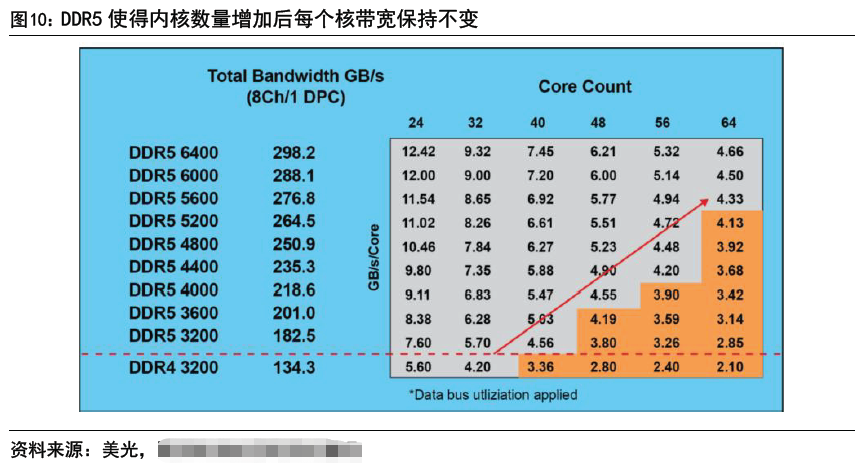

通常SDRAM在一个时钟周期内只传输一次数据,而DDR则是一个时钟周期内可传输两次。随着CPU内核数增加,为保证每个核的带宽不变,整体DDR的带宽(Bandwidth)及功耗要求不断提升,DDR由第一代升级至第五代DDR5。相比DDR4,DDR5数据传输速度与有效带宽翻倍。

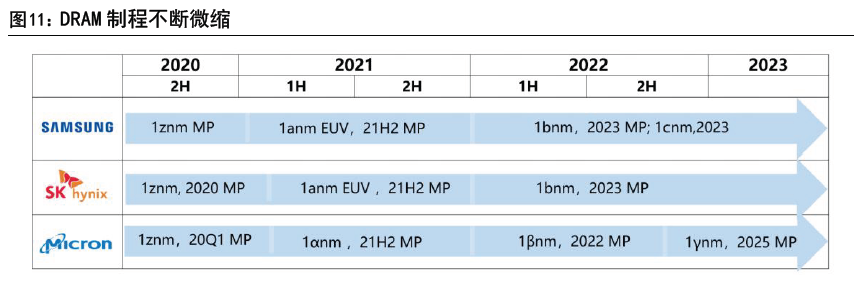

先进的工艺节点与封装技术的演进是DDR升级的核心要素。每个节点级数都代表芯片中晶体管和电容器的最小组件缩小,14年三星率先实现20nm量产(4Gb DDR3DRAM),

此后DRAM制程每两年代,从1Xnm(1nm-19nm)到1Ynm(14nm-16nm)到1Znm (12-14nm,DDR4X/5及LPDDR4X/5);22年美光推出了1BDRAM技术,该技术初步可使LPDDR5X效率提升15%。

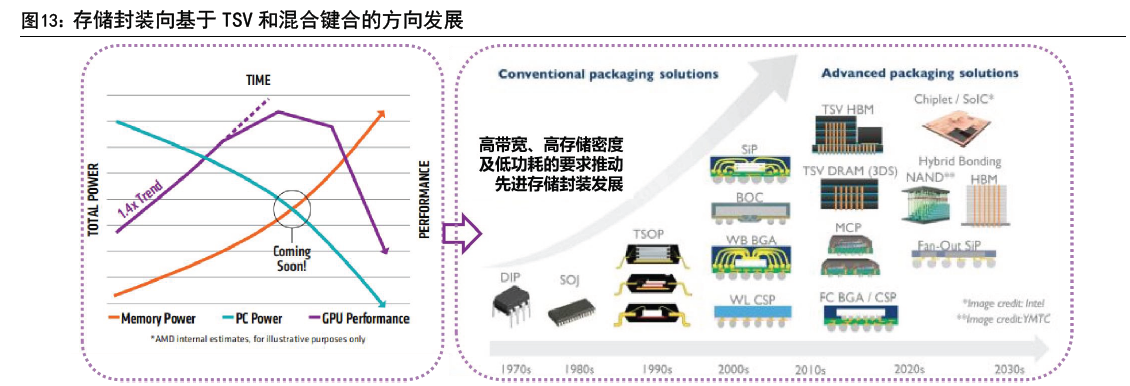

在此基础上,硅通孔(TSV)技术可实现DRAM芯片的多层堆叠,提升模块容量;例如三星DDR5利用TSV技术堆叠了8层16GBDRAM芯片,DDR5模块容量提升至512GB。

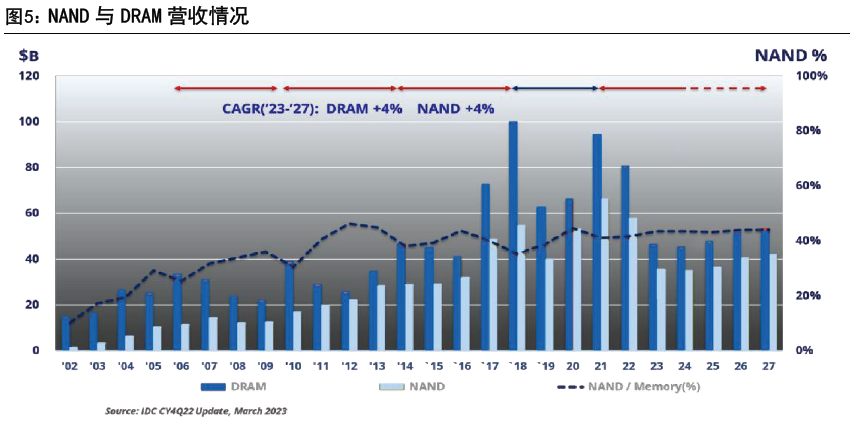

3、预计未来5年数据中心对DRAM的需求复合增速将超30%

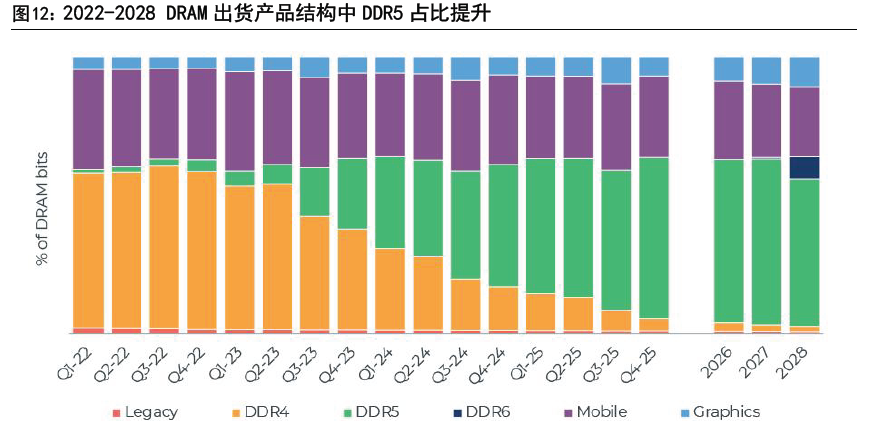

DDR5作为高性价比的内存形式将成为DRAM的主要出货类型,根据Yole及IDC 数据,尽管23年PC、服务器需求恢复有限,DDR5 渗透率提升较慢,随着AI、服务器及物联网带来的计算需求增加,未来五年,DRAM 需求将快速增长。

其中DDR5作为高性能低功耗的新一代产品,将广泛应用于大多数的计算场景中,成为主流产品,25年后渗透率将超60%。

尽管HBM (High Bandwidth Memory)在高度并行计算、计算机视觉AI等应用中有卓越的性能优势,但考虑其成本、内存灵活性等因素,DDR5将在较长时间内占据主要的内存应用市场。

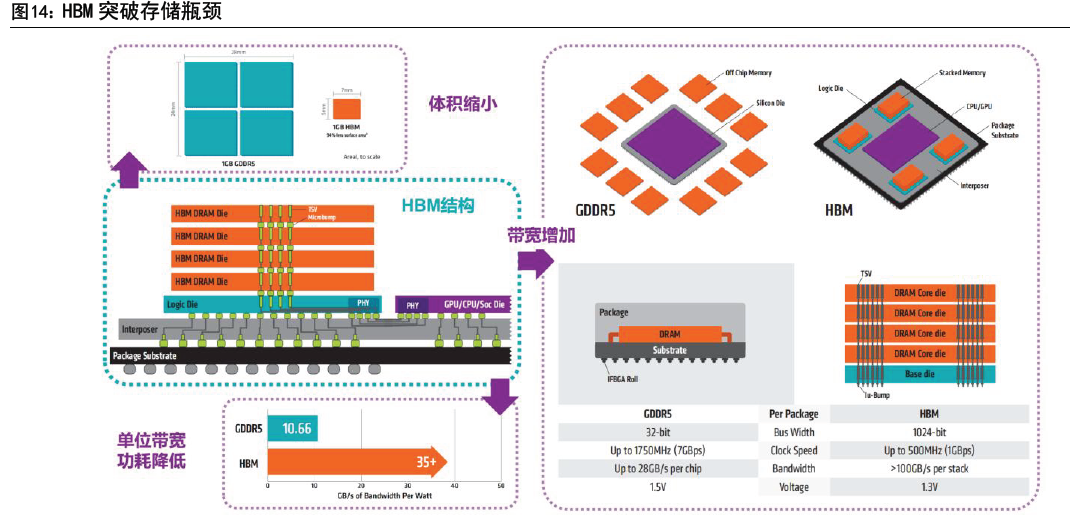

4、HBM为代表的新能内存

“内存墙”的限制将促进TSV(硅通孔)、混合键合为基础的先进内存封装技术26年占比将在20年基础上增加两倍以上。随着数据密集型应用不断增长,目前处理器算力超过存储芯片存取能力,内存和处理单元之间的数据传输带宽受限即受到“内存墙”的阻碍;

以HBM(高带宽存储器,High Bandwidth Memory)为代表的新型内存封装形式应运而生。根据 Yole 数据,2026年内存封装市场将增至198亿美元,其中TSV、混合键合等先进封装技术占比将由2020 年不到5%增至约18%。

根据Trendforce 数据,高端GPU 需求提升将拉动HBM23 年需求量增加58%,24年将再增加30%HBM是利用TSV和热压键合等技术将DRAM芯片进行堆叠并与GPU一起封装以实现更高的传输带宽的新型内存封装形式。

从传输位宽来看,通过该种互连方式,每层DRAM 芯片有两个128 bits通道,若堆叠4层DRAM芯片对应1024bits即1024个数据引脚;

若GPU周围配置4块该类型HBM内存,则总位宽为4096bits;相比GDDR5显存16通道对应512 bits大幅提升,适用于游戏和图形处理等高并行任务对带宽要求高的应用。

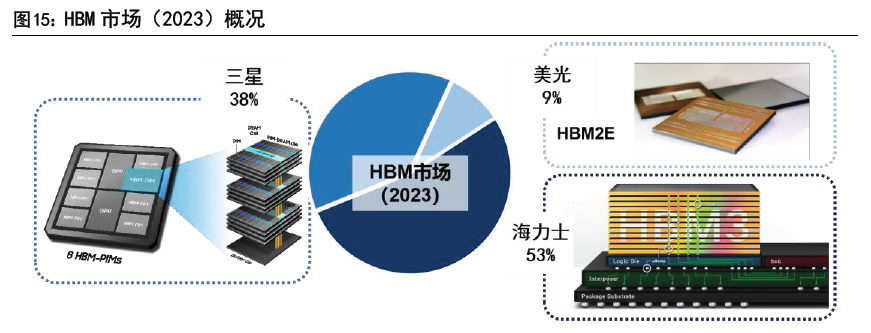

根据Trendforce 数据,HBM市场被海力士(占53%)、三星(占38%)和美光(占9%)三大内存原厂占据。2014年,AMD与海力士合作开发出了全球第一代HBM,随后海力士相继推出了HBM2、HBM2E、HBM3等产品,内存Die堆叠层数由4层增至12层,单颗HBM容量可达24GB;

此外,三星HBM3亦开始量产,并推出了HBM-PIM(存算一体)产品;美光HBM2E于21 年开始量产,随着NVIDIA GPU H100、A100采用了HBM2e、HBM3技术,HBM应用将逐步走向成熟,成为AI服务器与高端GPU的主要封装形式。

VIP复盘网

VIP复盘网