受益制程微缩&3D趋势,刻蚀设备成为第一大半导体设备

设备为IC制造第一大资本支出,全球芯片投资Capex预计2024年复苏

根据Gartner数据,集成电路制造设备投资一般占集成电路制造领域资本性支出的70%- 80%,且随着工艺制程的提升,设备投资占比也将相应提高——当制程达到14/16nm时, 设备投资占比可达85%。 芯片制造是集成电路制造过程中最重要、最复杂的环节,对应设备投资占比可达78%- 80%。 由于2021年和2022年全球集成电路投资过热以及2023年全球经济不景气,2023年全球芯 片投资Capex预计下降至1635亿美元,2024年有望开始复苏。

中国大陆连续四年成为全球最大半导体设备市场

根据SEMI数据,2024H1全球半导体设备销售额为532亿美元;其中,中国大陆半导体设备销售额为247亿美元,占比达46.43%,创历史新高,连续五年成为全球最 大半导体设备市场。 相比后道环节,前道晶圆制造技术难度更高,涉及工艺更繁杂,涵盖光刻、刻蚀、 薄膜沉积、清洗、离子注入、化学机械平坦等工艺,因此所需设备价值量更高、种 类更多。SEMI数据显示,2023年晶圆制造设备市场规模约占半导体设备总市场规 模的90%。 刻蚀工艺用于去除特定区域的材料来形成微小的结构和图案。随着集成电路线宽的 持续减小和3D集成电路的发展,刻蚀设备已跃居集成电路采购额最大的设备类型。 2023年刻蚀设备市场规模约210.44亿美元,占晶圆制造设备总市场规模的22%。

2018~2025年中国大陆新建晶圆厂项目预计为74座,占比位居全球第一

Gartner预计,2018-2025年全球新建晶圆厂项 目总数预计为171座,其中中国大陆为74座,占 比为43%,位居全球第一。 中国大陆74座新建晶圆厂项目中,有53座为12 寸晶圆项目;Foundry厂为主要建设厂商;目前 绝大多数项目均已开始建设;有35座项目将于 2024年后开始生产。

以中芯国际8寸/12寸产线为例,刻蚀设备数量占比约10%

根据芯思想研究院调研,截止2023年12月20日,中国大陆12 英寸、8英寸和6英寸及以下的硅晶圆制造线共有210条(不含 纯MEMS生产线、化合物半导体生产线和光电子生产线)。 建成12英寸晶圆厂45座,在建24座,规划兴建或改造13座, 全部产能合计420万片;建成8英寸晶圆厂34座,在建5座, 规划兴建或改造11座,全部产能合计220万片。 以中芯国际8寸/12寸产线为例,单条产线约有10%的设备为 刻蚀设备。

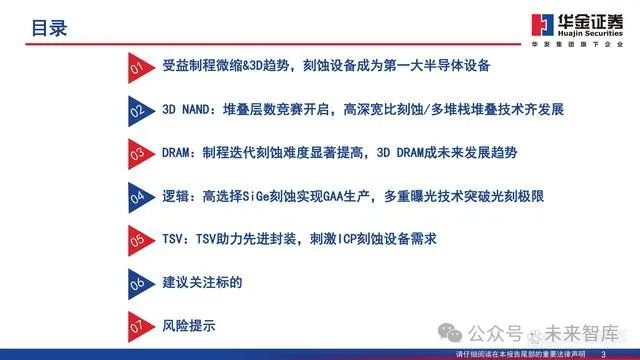

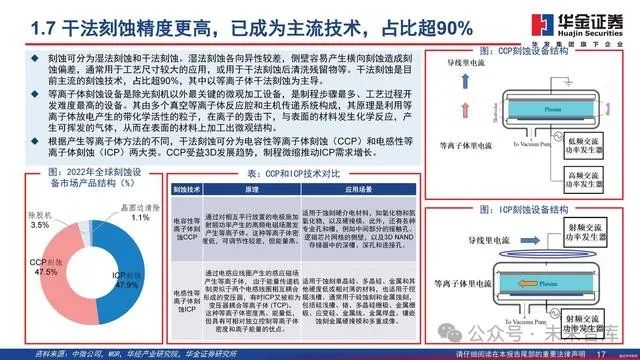

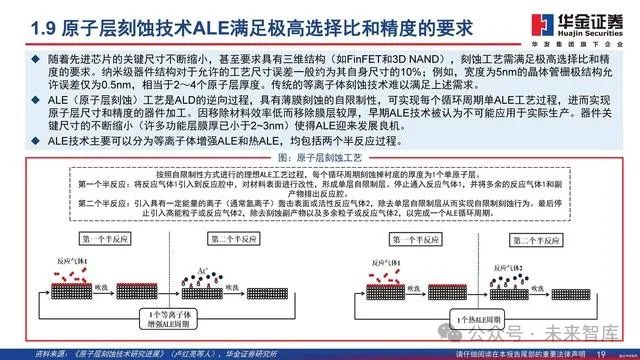

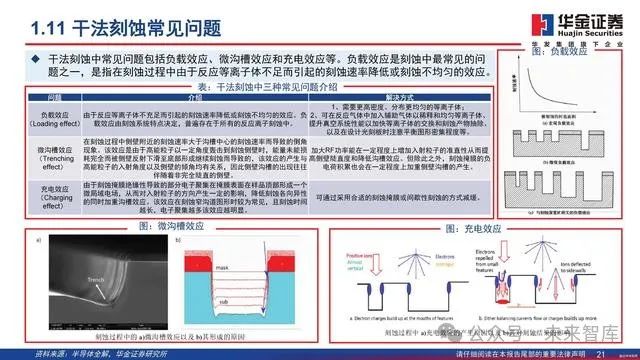

干法刻蚀精度更高,已成为主流技术,占比超90%

刻蚀可分为湿法刻蚀和干法刻蚀。湿法刻蚀各向异性较差,侧壁容易产生横向刻蚀造成刻 蚀偏差,通常用于工艺尺寸较大的应用,或用于干法刻蚀后清洗残留物等。干法刻蚀是目 前主流的刻蚀技术,占比超90%,其中以等离子体干法刻蚀为主导。 等离子体刻蚀设备是除光刻机以外最关键的微观加工设备,是制程步骤最多、工艺过程开 发难度最高的设备。其由多个真空等离子体反应腔和主机传递系统构成,其原理是利用等 离子体放电产生的带化学活性的粒子,在离子的轰击下,与表面的材料发生化学反应,产 生可挥发的气体,从而在表面的材料上加工出微观结构。根据产生等离子体方法的不同,干法刻蚀可分为电容性等离子体刻蚀(CCP)和电感性等 离子体刻蚀(ICP)两大类。CCP受益3D发展趋势,制程微缩推动ICP需求增长。

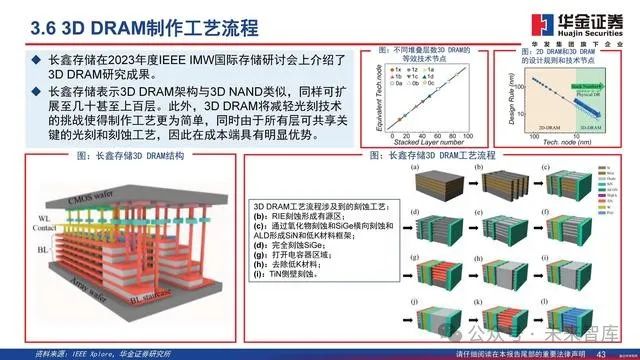

3D NAND:堆叠层数竞赛开启,高深宽比刻 蚀/多堆栈堆叠技术齐发展

3D NAND简介

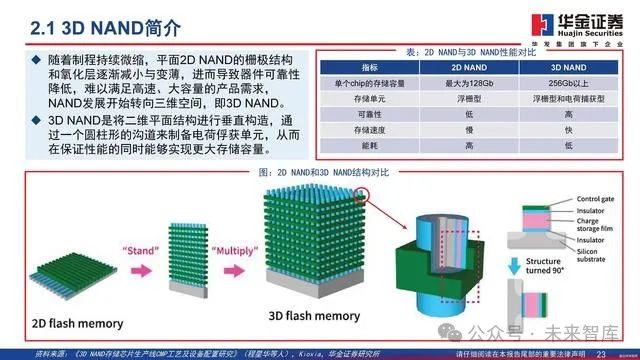

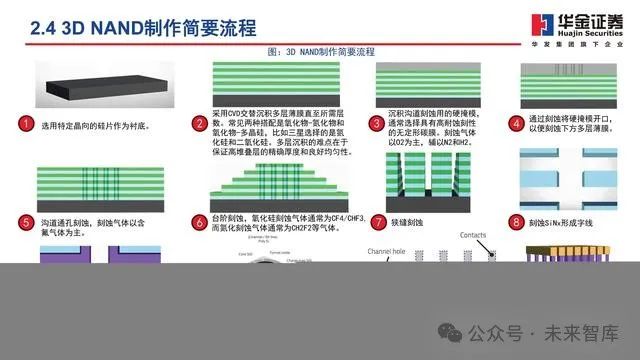

随着制程持续微缩,平面2D NAND的栅极结构 和氧化层逐渐减小与变薄,进而导致器件可靠性 降低,难以满足高速、大容量的产品需求, NAND发展开始转向三维空间,即3D NAND。 3D NAND是将二维平面结构进行垂直构造,通 过一个圆柱形的沟道来制备电荷俘获单元,从而 在保证性能的同时能够实现更大存储容量。

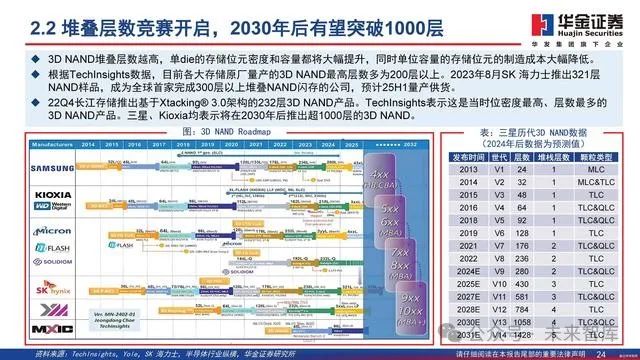

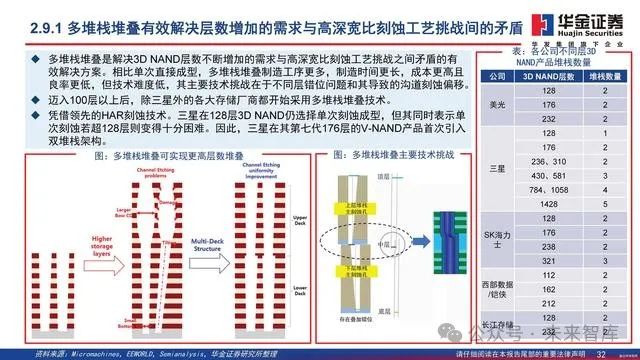

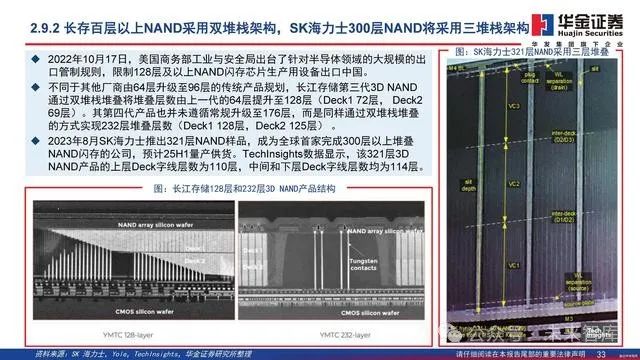

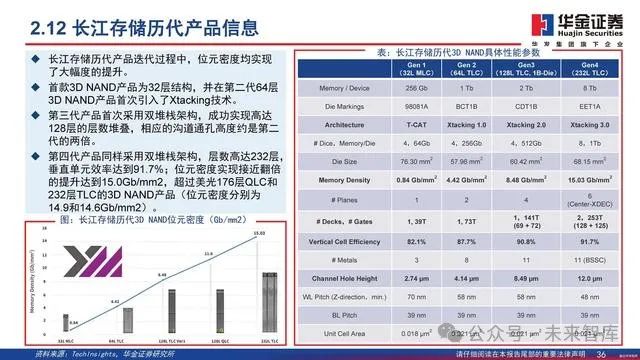

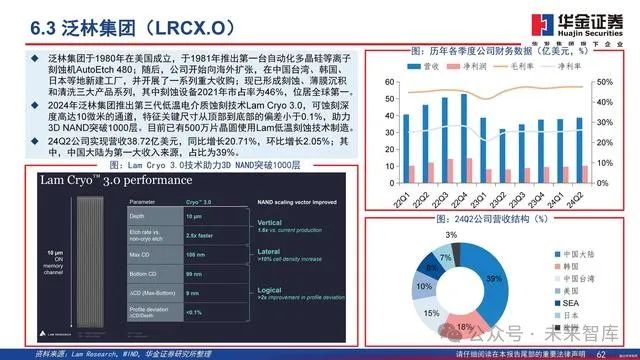

堆叠层数竞赛开启,2030年后有望突破1000层

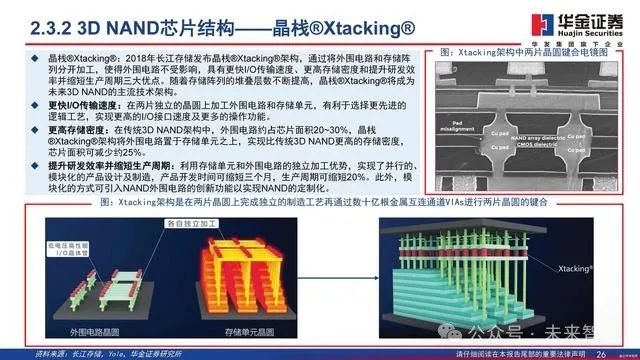

3D NAND堆叠层数越高,单die的存储位元密度和容量都将大幅提升,同时单位容量的存储位元的制造成本大幅降低。 根据TechInsights数据,目前各大存储原厂量产的3D NAND最高层数多为200层以上。2023年8月SK海力士推出321层NAND样品,成为全球首家完成300层以上堆叠NAND闪存的公司,预计25H1量产供货。 22Q4长江存储推出基于Xtacking® 3.0架构的232层3D NAND产品。TechInsights表示这是当时位密度最高、层数最多的3D NAND产品。三星、Kioxia均表示将在2030年后推出超1000层的3D NAND。

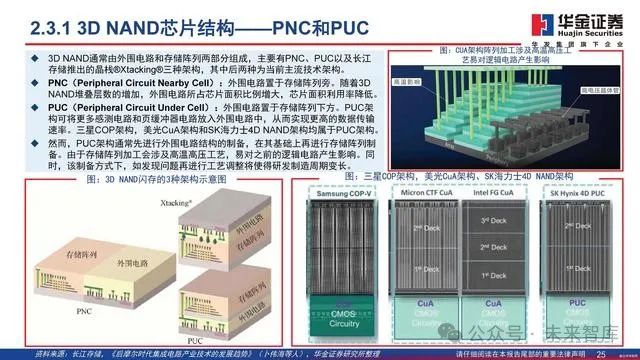

3D NAND芯片结构——PNC和PUC

3D NAND通常由外围电路和存储阵列两部分组成,主要有PNC、PUC以及长江 存储推出的晶栈®Xtacking®三种架构,其中后两种为当前主流技术架构。 PNC(Peripheral Circuit Nearby Cell):外围电路置于存储阵列旁。随着3D NAND堆叠层数的增加,外围电路所占芯片面积比例增大,芯片面积利用率降低。 PUC(Peripheral Circuit Under Cell):外围电路置于存储阵列下方。PUC架 构可将更多感测电路和页缓冲器电路放入外围电路中,从而实现更高的数据传输 速率。三星COP架构,美光CuA架构和SK海力士4D NAND架构均属于PUC架构。 然而,PUC架构通常先进行外围电路结构的制备,在其基础上再进行存储阵列制 备。由于存储阵列加工会涉及高温高压工艺,易对之前的逻辑电路产生影响。同 时,该制备方式下,如发现问题再进行工艺调整将使得研发制造周期变长。

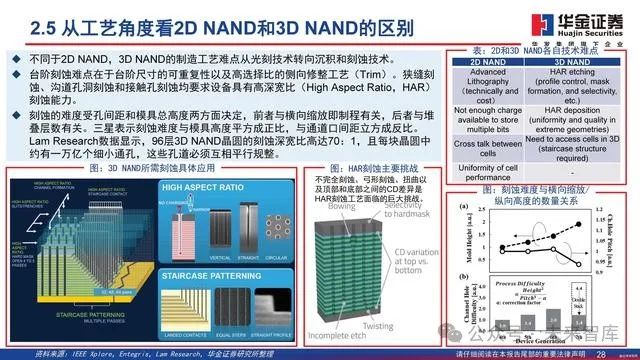

从工艺角度看2D NAND和3D NAND的区别

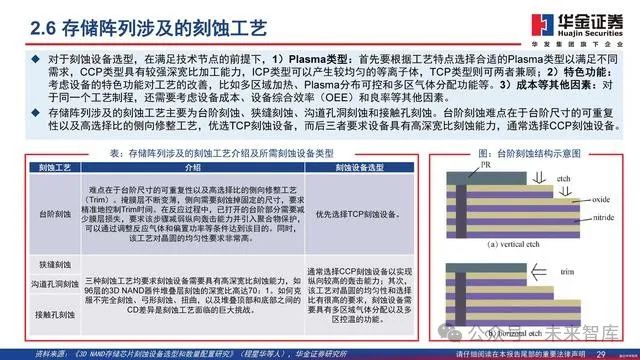

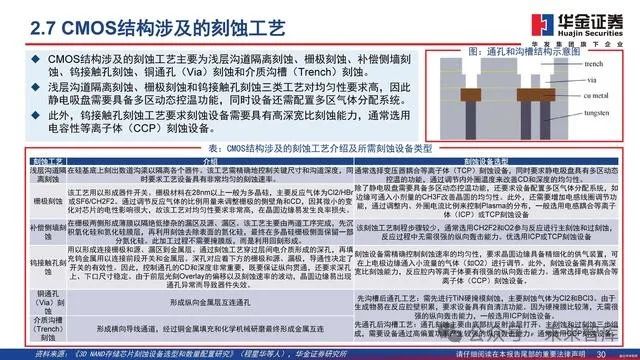

不同于2D NAND,3D NAND的制造工艺难点从光刻技术转向沉积和刻蚀技术。 台阶刻蚀难点在于台阶尺寸的可重复性以及高选择比的侧向修整工艺(Trim)。狭缝刻 蚀、沟道孔洞刻蚀和接触孔刻蚀均要求设备具有高深宽比(High Aspect Ratio,HAR) 刻蚀能力。 刻蚀的难度受孔间距和模具总高度两方面决定,前者与横向缩放即制程有关,后者与堆 叠层数有关。三星表示刻蚀难度与模具高度平方成正比,与通道口间距立方成反比。 Lam Research数据显示,96层3D NAND晶圆的刻蚀深宽比高达70:1,且每块晶圆中 约有一万亿个细小通孔,这些孔道必须互相平行规整。

DRAM:制程迭代刻蚀难度显著提高, 3D DRAM成未来发展趋势

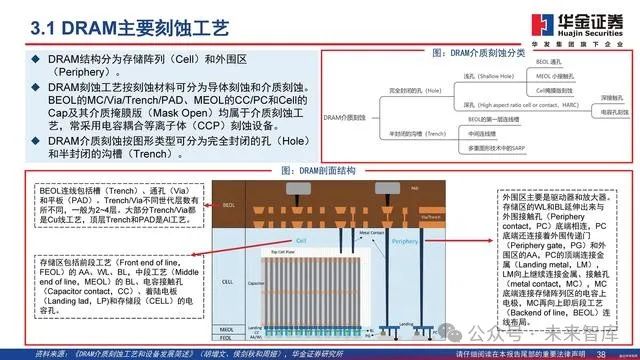

DRAM主要刻蚀工艺

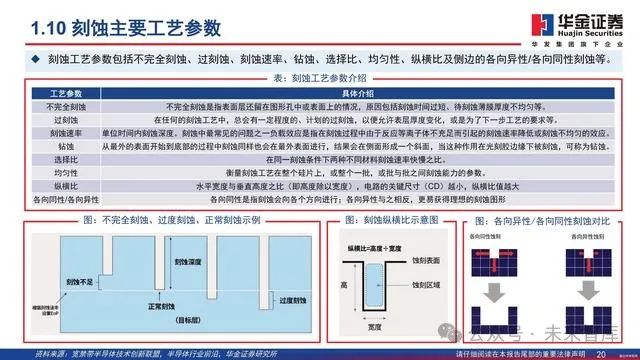

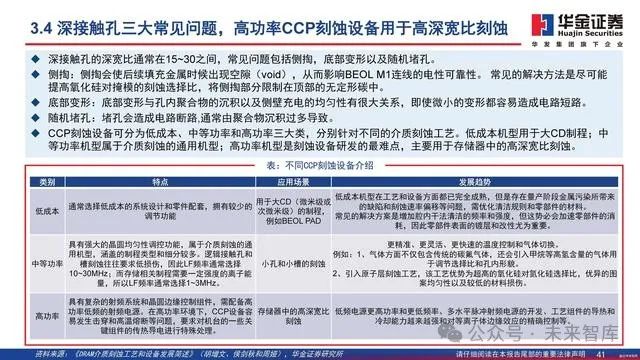

DRAM结构分为存储阵列(Cell)和外围区 (Periphery)。DRAM刻蚀工艺按刻蚀材料可分为导体刻蚀和介质刻蚀。 BEOL的MC/Via/Trench/PAD、MEOL的CC/PC和Cell的 Cap及其介质掩膜版(Mask Open)均属于介质刻蚀工 艺,常采用电容耦合等离子体(CCP)刻蚀设备。 DRAM介质刻蚀按图形类型可分为完全封闭的孔(Hole) 和半封闭的沟槽(Trench)。

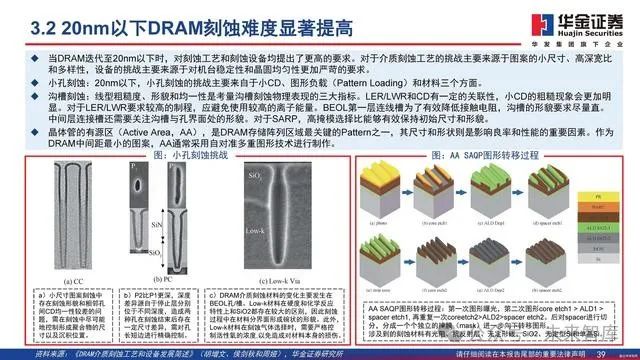

20nm以下DRAM刻蚀难度显著提高

当DRAM迭代至20nm以下时,对刻蚀工艺和刻蚀设备均提出了更高的要求。对于介质刻蚀工艺的挑战主要来源于图案的小尺寸、高深宽比和多样性,设备的挑战主要来源于对机台稳定性和晶圆均匀性更加严苛的要求。 小孔刻蚀:20nm以下,小孔刻蚀的挑战主要来自于小CD、图形负载(Pattern Loading)和材料三个方面。 沟槽刻蚀:线型粗糙度、形貌和均一性是考量沟槽刻蚀物理表现的三大指标。LER/LWR和CD有一定的关联性,小CD的粗糙现象会更加明显。对于LER/LWR要求较高的制程,应避免使用较高的离子能量。BEOL第一层连线槽为了有效降低接触电阻,沟槽的形貌要求尽量直。中间层连接槽还需要关注沟槽与孔界面处的形貌。对于SARP,高掩模选择比能够有效保持初始尺寸和形貌。 晶体管的有源区(Active Area,AA),是DRAM存储阵列区域最关键的Pattern之一,其尺寸和形状则是影响良率和性能的重要因素。作为DRAM中间距最小的图案,AA通常采用自对准多重图形技术进行制作。

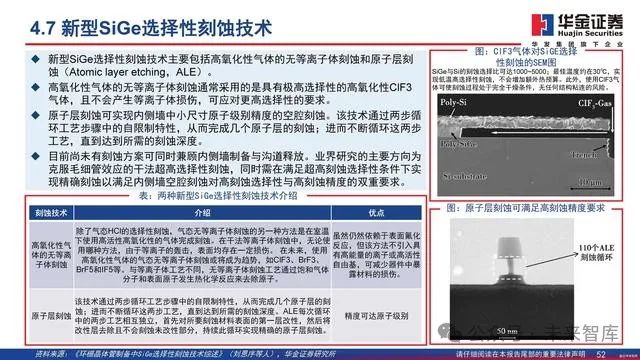

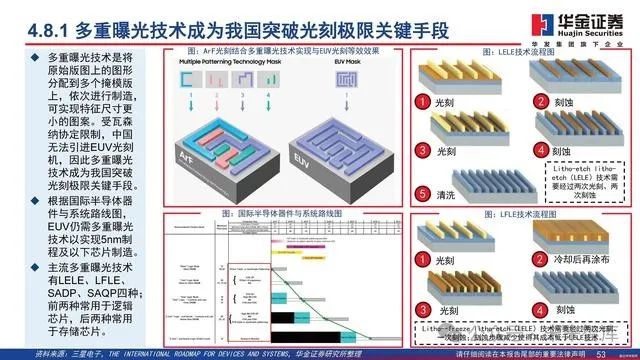

逻辑:高选择SiGe刻蚀实现GAA生产,多重 曝光技术突破光刻极限

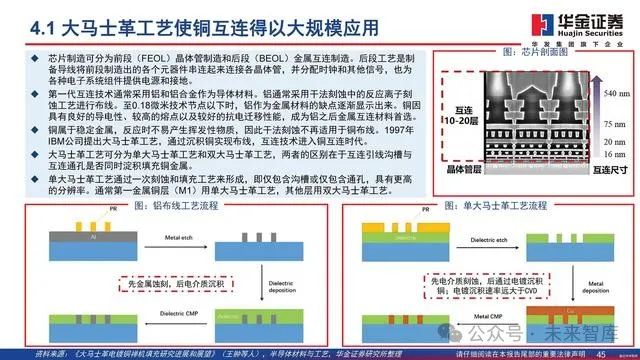

大马士革工艺使铜互连得以大规模应用

芯片制造可分为前段(FEOL)晶体管制造和后段(BEOL)金属互连制造。后段工艺是制 备导线将前段制造出的各个元器件串连起来连接各晶体管,并分配时钟和其他信号,也为 各种电子系统组件提供电源和接地。 第一代互连技术通常采用铝和铝合金作为导体材料。铝通常采用干法刻蚀中的反应离子刻 蚀工艺进行布线。至0.18微米技术节点以下时,铝作为金属材料的缺点逐渐显示出来。铜因 具有良好的导电性、较高的熔点以及较好的抗电迁移性能,成为铝之后金属互连材料首选。 铜属于稳定金属,反应时不易产生挥发性物质,因此干法刻蚀不再适用于铜布线。1997年 IBM公司提出大马士革工艺,通过沉积铜实现布线,互连技术进入铜互连时代。大马士革工艺可分为单大马士革工艺和双大马士革工艺,两者的区别在于互连引线沟槽与 互连通孔是否同时淀积填充铜金属。 单大马士革工艺通过一次刻蚀和填充工艺来形成,即仅包含沟槽或仅包含通孔,具有更高 的分辨率。通常第一金属铜层(M1)用单大马士革工艺,其他层用双大马士革工艺。

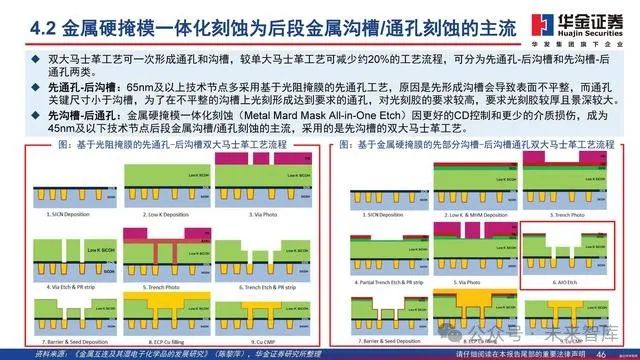

金属硬掩模一体化刻蚀为后段金属沟槽/通孔刻蚀的主流

金属硬掩膜一体化刻蚀(AIO-ET,All In One Etch)需在干法刻蚀机的同一个工艺腔体内一次完成,包括:①一次光刻完成沟槽形貌定义;②金属刻蚀腔完成金属掩膜刻蚀、去光刻胶,停在TEOS上,完成沟槽形貌刻蚀;③二次光刻完成通孔形貌定义;④干法刻蚀形成半通孔形貌 去光刻胶 沟槽&通孔一步刻蚀 盖帽层刻蚀。 金属硬掩膜一体化刻蚀工艺由于引入了全新硬掩膜材料(TiN)以及不同轮廓结构在一个工艺菜单条件下完成,使得一体化刻蚀工艺面临着诸多全新的挑战。TiN硬掩膜的引入除了会形成区别于传统工艺的刻蚀轮廓,反应生成物也由原先的C/H/O/F等易挥发的副产物变成更为复杂的含金属Ti的聚合物,这些金属副产物会沉积在产品表面以及工艺设备上影响产品的缺陷。由于金属硬掩膜一体化刻蚀工艺需要在一个工艺菜单条件下完成孔洞结构和沟槽结构的刻蚀,工艺步骤间的参数变化剧烈,这也会带来工艺上的诸多问题。

TSV:TSV助力先进封装,刺 激ICP刻蚀设备需求

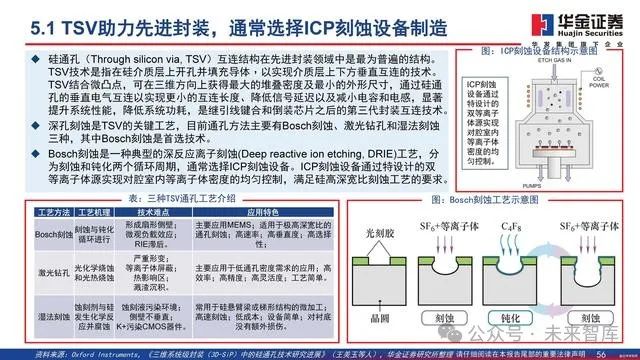

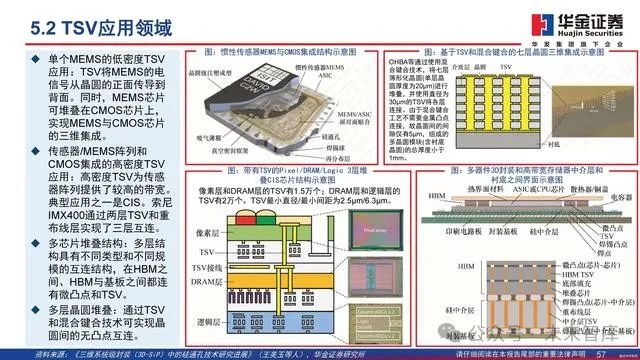

TSV助力先进封装,通常选择ICP刻蚀设备制造

硅通孔(Through silicon via, TSV)互连结构在先进封装领域中是最为普遍的结构。TSV技术是指在硅介质层上开孔并填充导体﹐以实现介质层上下方垂直互连的技术。TSV结合微凸点,可在三维方向上获得最大的堆叠密度及最小的外形尺寸,通过硅通孔的垂直电气互连以实现更小的互连长度、降低信号延迟以及减小电容和电感,显著提升系统性能,降低系统功耗,是继引线键合和倒装芯片之后的第三代封装互连技术。 深孔刻蚀是TSV的关键工艺,目前通孔方法主要有Bosch刻蚀、激光钻孔和湿法刻蚀三种,其中Bosch刻蚀是首选技术。 Bosch刻蚀是一种典型的深反应离子刻蚀(Deep reactive ion etching, DRIE)工艺,分为刻蚀和钝化两个循环周期,通常选择ICP刻蚀设备。ICP刻蚀设备通过特设计的双 等离子体源实现对腔室内等离子体密度的均匀控制,满足硅高深宽比刻蚀工艺的要求。

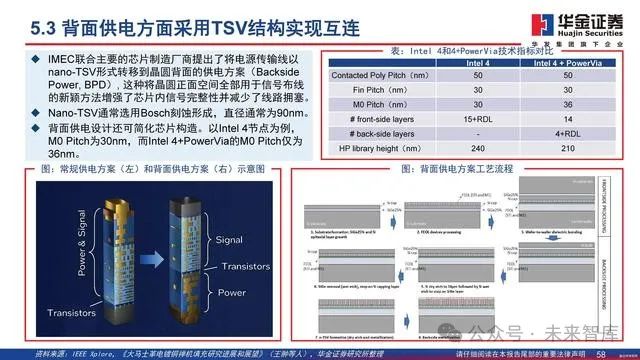

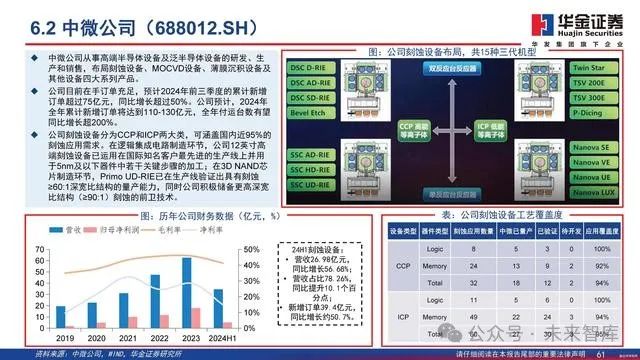

背面供电方面采用TSV结构实现互连

IMEC联合主要的芯片制造厂商提出了将电源传输线以 nano-TSV形式转移到晶圆背面的供电方案(Backside Power, BPD), 这种将晶圆正面空间全部用于信号布线 的新颖方法增强了芯片内信号完整性并减少了线路拥塞。 Nano-TSV通常选用Bosch刻蚀形成,直径通常为90nm。 背面供电设计还可简化芯片构造。以Intel 4节点为例, M0 Pitch为30nm,而Intel 4 PowerVia的M0 Pitch仅为 36nm。

报告节选:

上述文章报告出品方/作者:华金证券,孙远峰、王海维、吴家欢;仅供参考,投资者应独立决策并承担投资风险。

VIP复盘网

VIP复盘网